# System-on-Chip Meets Systems Engineering

A Simulation-Driven Approach

#### Stephan van Beek

Consulting Application Engineer MBSE/SoC/FPGA

#### Christoph Kammer

Senior Application Engineer **DevOps**

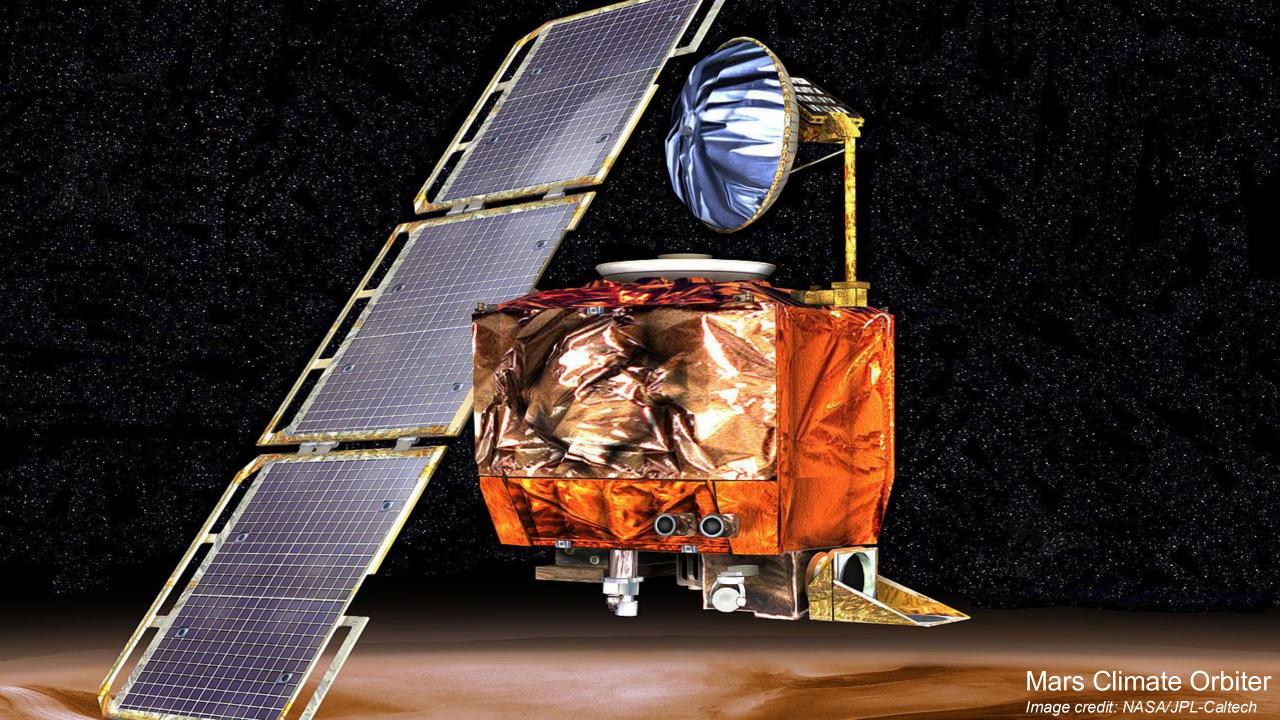

The biggest problem was not the unit mismatch itself, but the failure to detect and correct this mistake

1997

2008

2025

FPGAs bigger and better FPGAs

SoC = FPGA + ARM

technology-

logic interfaces

algorithms

advanced algorithms

people

1 engineer

multiple engineers

multidisciplinary team

process

schematic VHDL

Model-Based Design (MBD)

MBD + MBSE??

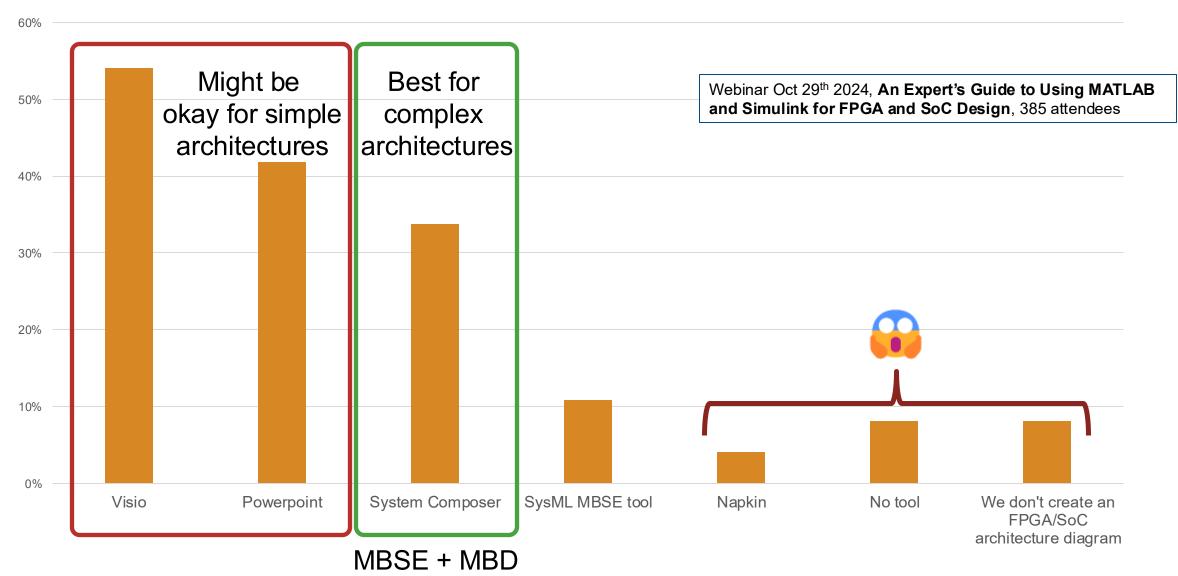

## How do you create your FPGA architectural block diagrams?

# Challenges ► complexity How do models and simulation help?

#### Top-down design processes

- Functional decomposition

- No simulation needed early, but ..... later you will need simulation

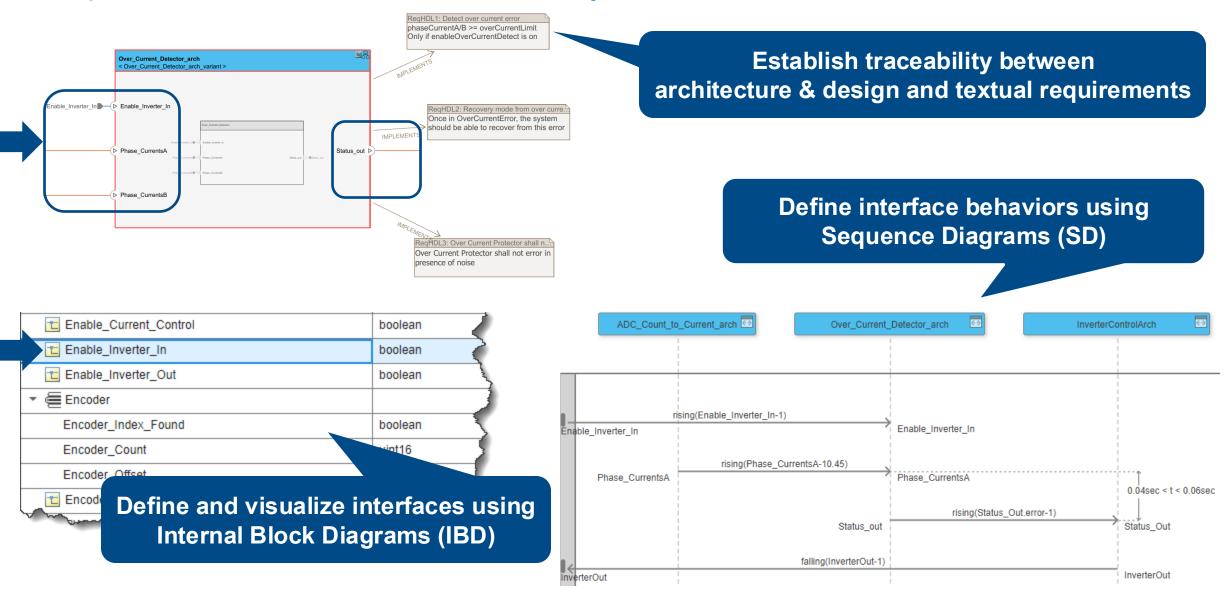

#### Go Beyond Textual Requirements

- Use expressiveness of requirement models and trade studies

- Use views to put stakeholder discussions in context

Validate compliance to requirements through simulation

#### Deployment

Generate RTL code from architecture + design models

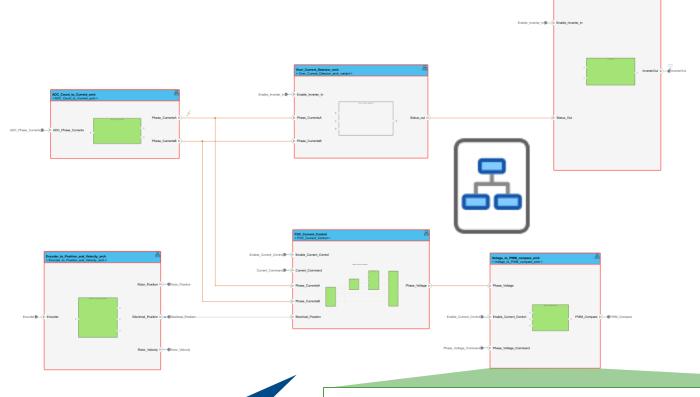

Model-Based Systems Engineering + Model-Based Design

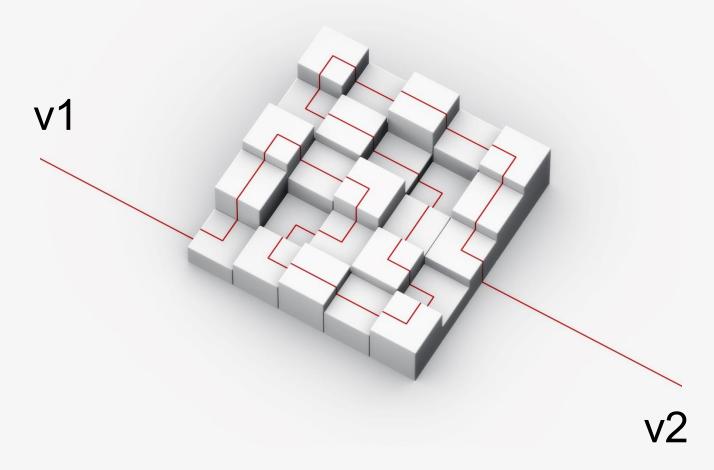

Top-down

Bottom-up

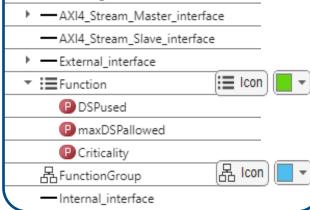

Custom Profiles

LogicalProfile

AXI4\_Light\_interface

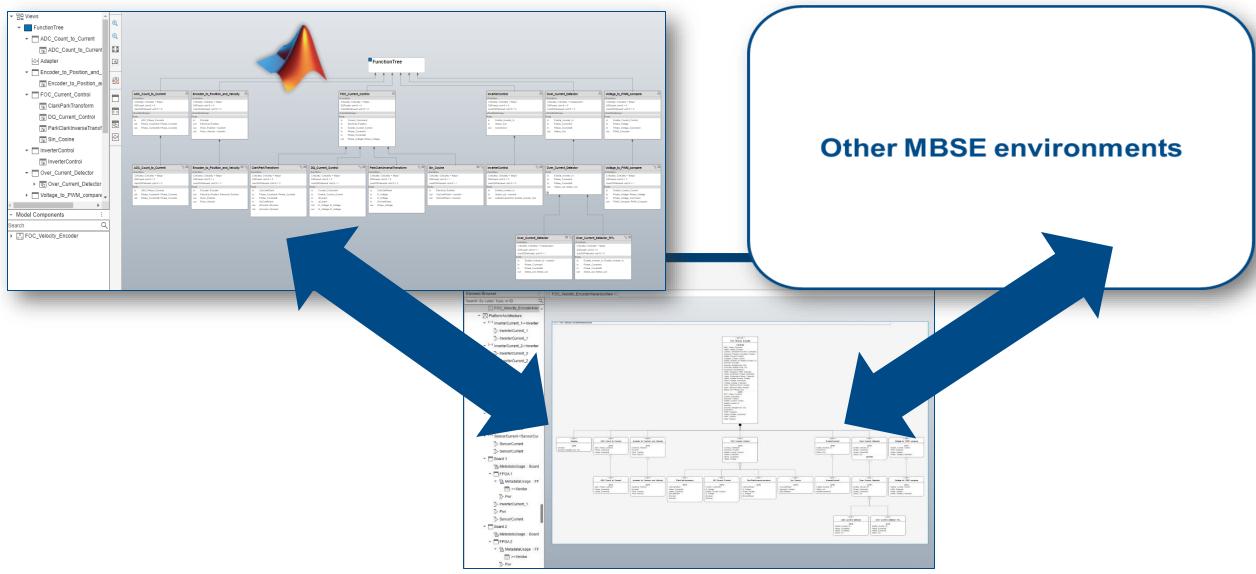

Integrate MBD with MBSE

#### Requirements: Textual, Traceability, Interfaces, Interactions

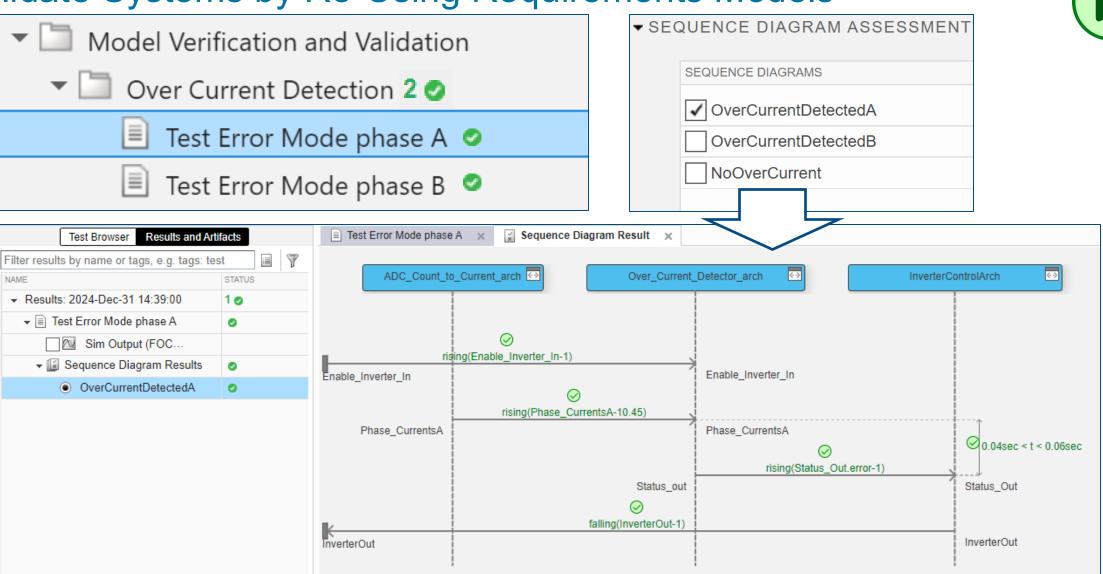

## Validate Systems by Re-Using Requirements Models

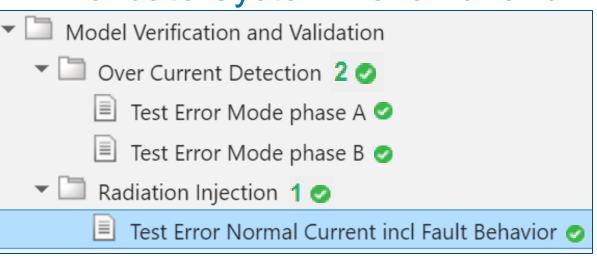

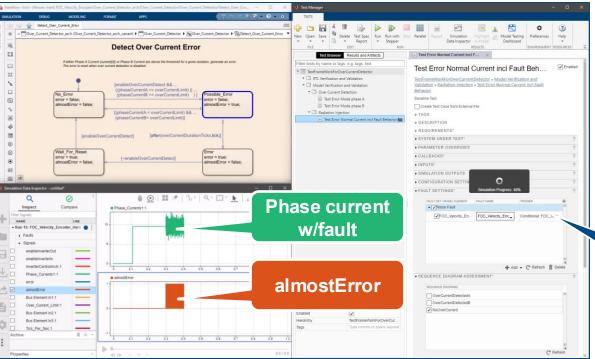

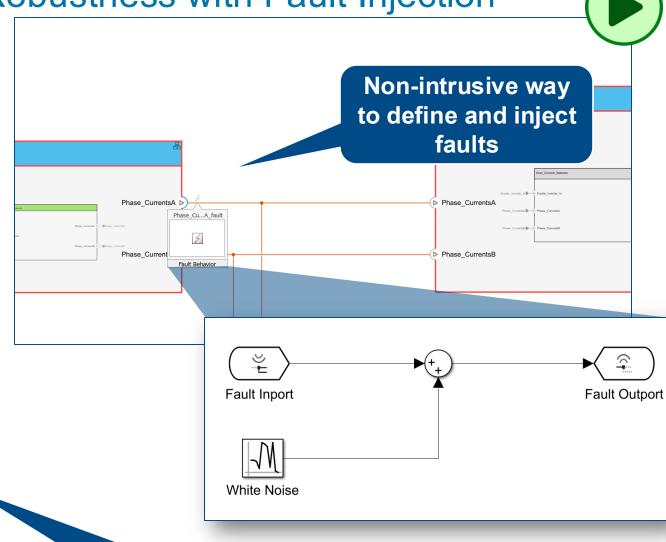

Validate System Behavior and Robustness with Fault Injection

Analyze impact of faults using simulation

#### Generate HDL code from System Architecture incl Detailed Models

The Road Ahead: SysML v2 and the Future of FPGA/SoC Development

## **Automation and Interoperability**

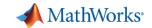

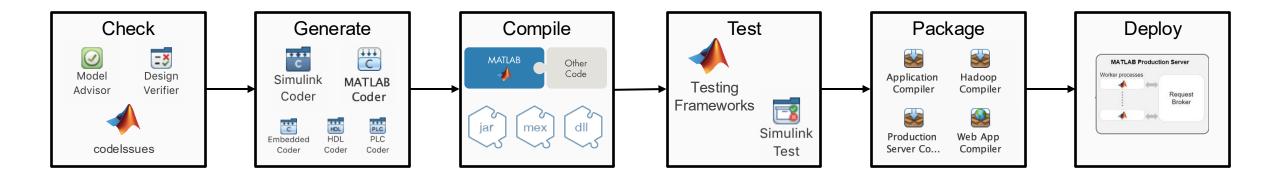

#### DevOps Automation to Ensure Consistent Build Processes

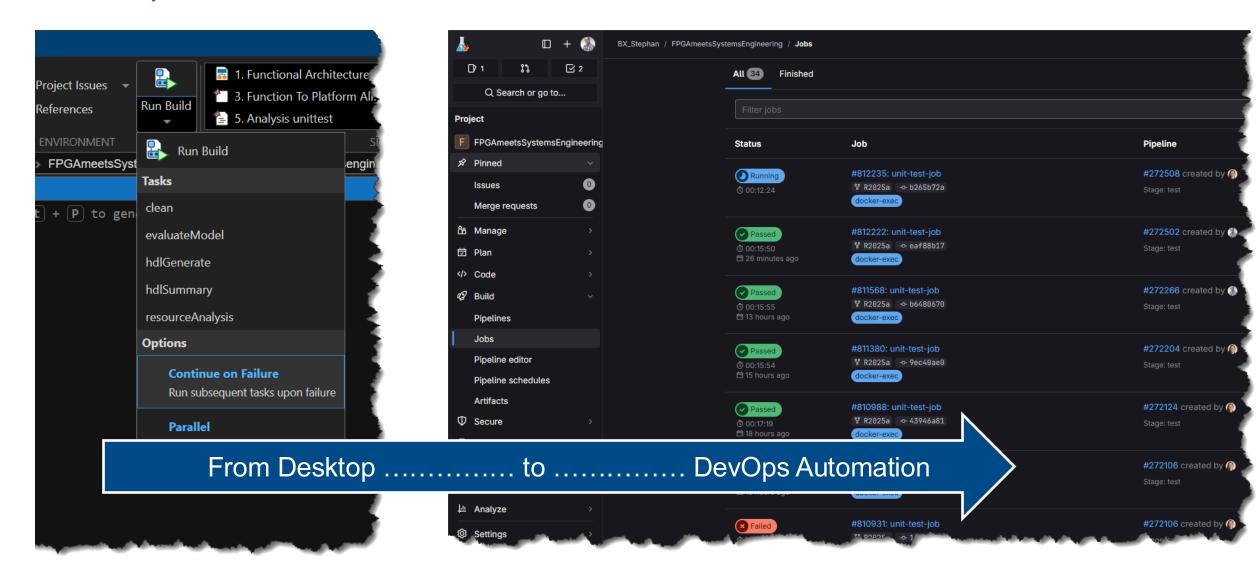

## Automate Locally or in CI with Buildtool

MATLAB has a growing list of capabilities that necessitate build tasks, resulting in more ad hoc scripts

The MATLAB Build Tool is a build system that provides a standard programming interface to create and run tasks in a uniform and efficient way

## Continuous Integration, Delivery and Deployment (CD)

### What is SysML?

#### SysML is used for:

- Modeling complex systems

- Visualizing system architecture

- Describing system behavior

- Verifying system requirements

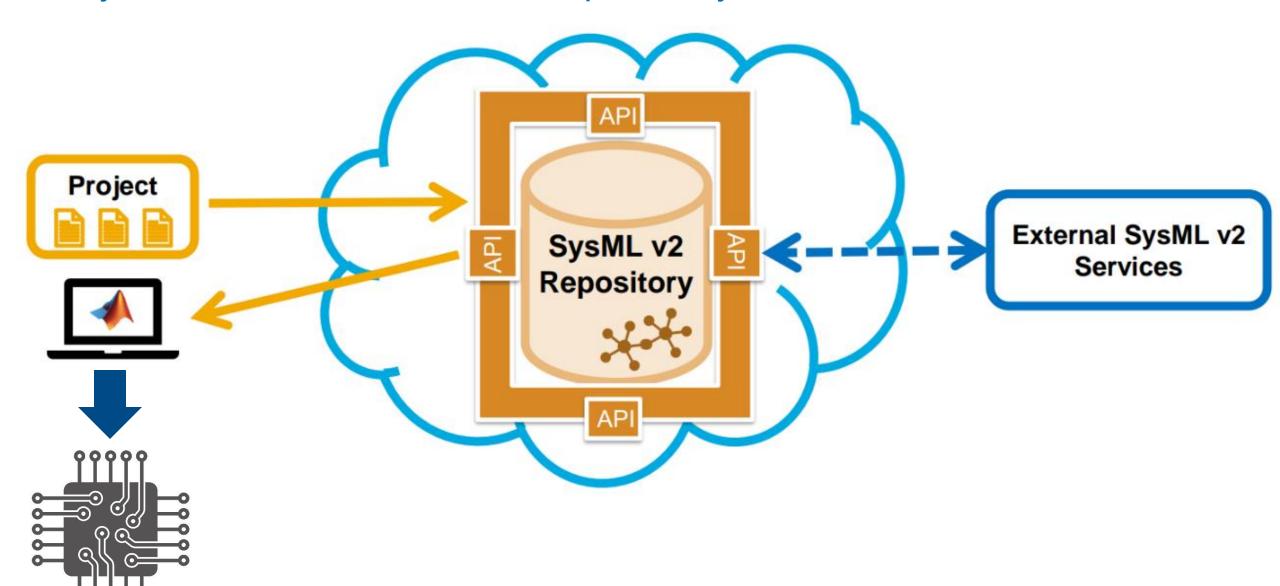

#### SysMLv2 and Enhanced Interoperability

#### Interoperability in Action

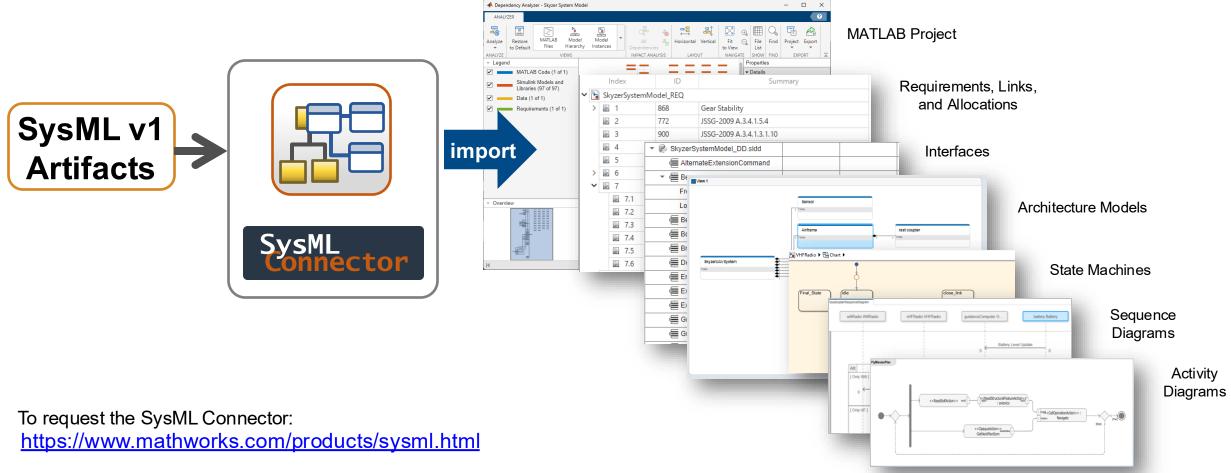

#### Where do I start with SysMLv1?

Use the SysML Connector to import your SysMLv1 model into MATLAB

#### **MathWorks Artifacts**

### Concluding remarks

Architecture

Design

**Simulation**

The main FPGA challenge lies in architecture, often informal and overlooked. A tool is needed to generate RTL directly from the architecture + design in a single model, making it the single source of truth.

- Adam Taylor, Adiuvo -- well known FPGA/SoC influencer and blogger

**Automation**

Interoperability

#### Questions?

More information